# Low Voltage and Low Complexity Temperature Compensated CMOS Circuit

Navid Alaie Sheini<sup>1</sup>, NimaAhmadpoor<sup>2</sup>

<sup>1</sup>Dept. of Electrical Engineering, Shahid Chamran University, Ahvaz, Iran <sup>2</sup>Dept. of Electrical Engineering, Mahshahr branch, Islamic Azad University, Mahshahr, Iran

# ABSTRACT

A 0.9Volt temperature compensated circuit is designed in the standard .18µm CMOS TSMC technology. This circuit is suitable for voltage reference application and is useful for a lower and greater supply voltage and submicron technology of CMOS. No BJT and resistor are used in this structure and the circuit consists of just eleven transistors. Some of CMOS transistors of the proposed circuit work in weak inversion region, which lead to realization of low voltage circuit and another work in strong inversion. The circuit offers a new temperature compensation methods can be used in many sensitive analog systems. This is simulated with 0.18µm TSMC technology. The technology. The technique which implement in this circuit is producing a current depends on  $v_T^2$  and  $\mu$ . But finally by injecting this current to a sub-threshold transistor the temperature range from -20°C to 180°C with power dissipation around 1.53 µwatt at 25°C. Also the circuit is examined in 1.1Volte supply voltage that results the temperature coefficient is changed to 4.5  $\frac{\text{PPIM}}{\text{C}}$

**KEYWORDS:** sub-threshold, voltage reference, temperature compensation, supply voltage, temperature coefficient

## **INTRODUCTION**

Reference voltages are important stages in many types of circuits such as: mixed signal circuits, ADCs, DACs, sensors and data acquisition and voltage regulators.

In the last few decades, research has been carried out in temperature dependence correction for voltage reference circuits. Furthermore, new available techniques and technology make it feasible to achieve low voltage, low power and low complexity.

The traditional voltage references, with curvature temperature correction, were implemented by BJTs. However because of the nonlinearity of temperature dependence these voltage references don't have very good temperature coefficient independency and because of silicon bandgap voltage 1.25v, which exceeds 1-V, there aren't suitable for low voltage applications. BJT-based voltage references have several hundred PPM/°C and aren't appropriate for accurate applications [1, 2]

Another technique that was used in voltage reference is implementing BJT with CMOS technology to reduce the process complexity [3]. But, parasitic BJT transistors because of poor match of MOS devices don't have good respect. And these band gap references because of silicon band gap voltage and input common mode voltage which is needed for internal amplifier circuit aren't low voltage, either. Some techniques have been implemented for achieving sub-1V band gap references. These techniques are resistive subdivision [4, 5], low-threshold voltage device [6], BiCMOS process [7] and DTMOST device [8]. For achieving low temperature dependence band gap voltage reference other technique were offered such as exponential temperature compensation [9], piecewise-liner curvature correction [10], which have more complexity in circuit designing.

Another technique is using MOS transistor which works in saturation or sub-threshold regions. In some circuits all MOS transistor work in saturation region and uses resistor. In better circuits in this type, temperature dependence of resistors is considered such as  $\mu$  and V<sub>T</sub> [11]. In another circuits some of MOS transistors work in saturation and others work in sub-threshold and with (or without) resistor [12, 13]. By using sub-threshold region, we can use lower supply voltage for circuits simply but temperature compensation formula will be more complex mathematically. The remaining problem in using resistor in such circuit is low temperature compensation accuracy and more complexity in design [14]. These cause appetency to only-CMOS techniques without resistor. To achieve low voltage and low power circuit, purposed using transistor in sub-threshold region [13, 15].In this work design a voltage reference circuit only with MOS transistor without resistor. Because some of transistors work in sub-

\*Corresponding Author: Navid Alaie Sheini Dept. of Electrical Engineering, Shahid Chamran University Ahvaz, Iran, number:00989163015235

threshold, the voltage supply is under 1 volt. And another advantage of the purposed circuit is involving fewer transistors than other circuits [15]. The number of transistors in this circuit is eleven MOS only and no additional component.

#### I. The Proposed Voltage Reference Circuit

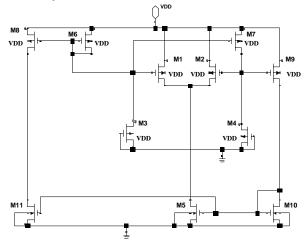

The complete circuit of proposed voltage reference is shown in Figure 1. This circuit consists of three parts: main part, bias transistors and current mirrors and output stage.

#### A. Main part

Main part circuit consists of M1 to M4, which two of which operate in weak-inversion and the rest operate in strong inversion. M1 and M2 are the transistors that operate in strong inversion with equation (1).

$$I_{D} = \frac{1}{2} \mu_{P} C_{OX} \frac{W}{L} (V_{SG} - |V_{thp}|)^{2}$$

(1)

Both drain and source of M1 connected to M2 pairs. This idea will reject variation effect of  $V_{DS}$  for the transistors. M3 and M4 work in weak inversion region. The relationship between voltage and current for PMOS in weak-inversion region is given by equation (2) [5].

$$I_D = \mu_P C_{OX} V_T^2 \frac{W}{L} \sqrt{\frac{q\varepsilon_{Si} N_{CH}}{2\varphi_B}} \exp(\frac{V_{SG} - |V_{thp}|}{nV_T})$$

(2)

One loop that passes through gate-source connect of transistors M1-M4 can be seen. It will be discussed that this loop can produce a current respect to  $\mu_p V_T^2$ .

Figure 1. Circuit schematic of the proposed voltage reference

#### **B.** Bias and Current Mirror

M6 and M7 are used for M3 and M4 biasing. These transistors (M6 and M7) generate same currents which are injected into M3 and M4. M8 and M9 are mirrored and have proportional current to M6 and M2. M6 current is depended to M1 current.

## C. Output Stage

M8 and M9 currents are injected to M10 and M11 which are mirrored. M10 is output transistor. This transistor is diode connected and operates in weak inversion with equation (2)

# II. Principle of Reduce Temperature Dependence

As it shown in Figure 1, we can write: V = V

$$V_{GS1} + V_{GS3} = V_{DI}$$

$V_{GS2} + V_{GS4} = V_{DD}$

Subtraction of above equations results:

$$V_{GS1} - V_{GS2} = V_{GS4} - V_{GS3}$$

(3)

$V_{GS1}$  and  $V_{GS2}$  are gate-source voltage for transistors M1 and M2 which operate in saturation region with equation(1). M3 and M4 are operating in sub-threshold region with equation (2). By superseding transistors equations in equation (3) can reach equation (4):

$$\sqrt{\frac{2Id_1}{\mu_p C_{ox}} (\frac{W}{L})_1} - \sqrt{\frac{2Id_2}{\mu_p C_{ox}} (\frac{W}{L})_2}} = nV_T Ln[\frac{(W/L)_3 Id_4}{(W/L)_4 Id_3}]$$

(4)

But Id1 and Id2 are related together with equation (5) and (6)

$$Id_1 + Id_2 = Id_5 \tag{5}$$

$$Id_{5} = \frac{(W/L)_{5}(W/L)_{9}}{(W/L)_{10}(W/L)_{2}}Id_{2}$$

(6)

By elimination of Id5 in these equations can reach to equation (7):

$$Id_{1} = \left[\frac{(W_{L})_{5}(W_{L})_{9}}{(W_{L})_{10}(W_{L})_{2}} - 1\right]Id_{2}$$

(7)

Simply can see:

$$Id_{3} = \left[\frac{(W/L)_{6}}{(W/L)_{7}}\right]Id_{4}$$

(8)

$$Id_{10} = \left[\frac{(W/L)_{10}}{(W/L)_2}\right]Id_2$$

(9)

And finally by replacement in equation (4) can reach equation (10):

$$Id_{2} = \mu_{p}C_{OX}n^{2}V_{T}^{2}\left[\frac{Ln\frac{(W_{L})_{3}(W_{L})_{7}}{(W_{L})_{4}(W_{L})_{6}}}{\frac{\sqrt{2}K_{1}}{(W_{L})_{1}} - \frac{\sqrt{2}}{(W_{L})_{2}}}\right]^{2}$$

(10)

Where *K*<sub>1</sub>is:

$$K_{1} = \frac{(w/l)_{s}(w/l)_{9}}{(w/l)_{10}(w/l)_{2}} - 1$$

(11)

Output transistor is M10 which work in sub-threshold region and it has current: Id10 which is related to Id2 by equation (9).  $V_{GS_{10}}$  Is output voltage of circuit and by using previous equations can easily find it:

$$V_{REF} = V_{GS_{10}} = |V_{th_N}| + n(\ln K_2)V_T$$

(12)

Where

$$K_{2}$$

is  $\frac{K_{3}}{(W/L)_{10}\sqrt{\frac{q\varepsilon_{Si}N}{2\phi_{B}}}}$  and  $K_{3}$  is equal to:

$$K_{3} = \left[\frac{Ln \frac{(W/L)_{3}(W/L)_{7}}{(W/L)_{4}(W/L)_{6}}}{\frac{\sqrt{2}K_{1}}{(W/L)_{1}} - \frac{\sqrt{2}}{(W/L)_{2}}}\right]^{2}$$

(13)

And  $V_{th_N}$  is threshold voltage of M10, n is sub threshold slope factor and  $V_T$  is thermal voltage.  $K_2$  is a variable which is depend on aspect values of transistors. Both  $V_T$  and  $V_{th_N}$  have temperature dependence but with two opposite slope. By tuning aspect values can generate a factor for  $V_T$  which can cancel temperature dependency of  $V_{th_N}$

#### **III. SIMULATION RESULT**

The Hspice simulation with 0.18µ TSMC technology was used for simulation. Simulation results have been studied for two supply voltage and the temperature range was selected from -20°C to 180°C for both of them.

In the first simulation supply voltage is VDD=.9v. The aspect values of transistors were tuned to reach the lowest temperature affect in output voltage. In this condition according to equation (10),  $Id_2$  is related to  $UV^2$

to  $\mu_p V_T^2$ .

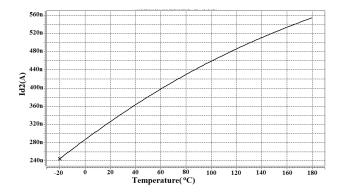

Furthermore, both  $\mu_p$  and  $V_T$  have temperature dependency:  $\mu_p \propto T^m$  where T is temperature and 'm' is constant near  $\frac{-3}{2}$  and  $V_T \propto T$  as result  $Id_2 \propto \mu_p V_T^2 \propto \sqrt{T}$ . Figure 2 shows the HSPIC simulation of  $Id_2$  vs. temperature.

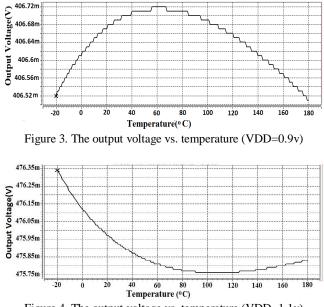

The simulation results show that the proposed voltage reference generates a mean reference voltage of about 406.62mv. The important MOS parameters used in this simulation is Vth(M10) which is equal to 480mv ,the simulated temperature coefficient of the voltage reference is TCR=2.46 PPM/  $^{\circ}C$ , for the extended temperature range of  $-20^{\circ}C$  <T<180  $^{\circ}C$ . Figure 3 shows the output voltage vs. temperature with VDD=.9v.

The second simulation is done by changing supply voltage to VDD=1.1v. The output voltage is shown in figure (4). The average output voltage in this condition is 476mV and the temperature coefficient in this condition was increasing to TCR=6.3 PPM/  $^{\circ}C$  for the extended temperature range of -20  $^{\circ}C < T < 180^{\circ}C$ , however temperature dependency remained low. Figure 4 shows the output voltage vs. temperature with VDD=1.1v.

Figure 2. The M2 drain current vs. temperature (VDD=0.9v)

Figure 4. The output voltage vs. temperature (VDD=1.1v)

## **IV.** Conclusion

A low voltage CMOS circuit with only eleven standard CMOS transistors and without extra element has been described for voltagereference application, which need low temperature dependency. Temperature compensation theory was studied with HSPICE simulation which illustrated very good TC, near 2.5 PPM/°C, compared to other works and it has wide temperature range, from  $-20^{\circ}C$  to  $180^{\circ}C$ . This circuit is low power too, with power consumption:  $1.53 \mu Watt$  at 25°C through 0.9V supplyvoltage. In Table 1 this work has been compared with some others. This table shows the advantages of proposed circuit especially lower TC in wider temperature range.

|      | Process    | Temp<br>Range(° <sub>C</sub> ) | <b>ТС</b><br><b>РРМ/</b> ° <i>с</i> | Extra<br>device | Minimum<br>Supply(V) | Power<br>(µWatt) |

|------|------------|--------------------------------|-------------------------------------|-----------------|----------------------|------------------|

| [13] | 0.18 µm    | -40 to 85                      | 4.6                                 | none            | 0.58V                | 0.0348           |

|      | CMOS       |                                |                                     |                 |                      | 0.58V            |

| [15] | 0.13<br>µт | -55 to 90                      | 5                                   | none            | 0.76V                | 0.471<br>@       |

|      | CMOS       |                                |                                     |                 |                      | 0.76V            |

| [14] | 0.18<br>µт | 0 to 130                       | 19                                  | resistor        | 0.7V                 | 119              |

|      | CMOS       |                                |                                     |                 |                      | @<br>0.7V        |

| [12] | 0.6<br>µт  | -40 to 120                     | 37.4                                | resistor        | 1.4V                 | 5.6              |

|      | CMOS       |                                |                                     |                 |                      | @<br>1.4V        |

| This | 0.18       | -20 to 180                     | 2.5                                 | none            | 0.9V                 | 1.53             |

| work | µm<br>CMOS |                                |                                     |                 |                      | @<br>0.9V        |

#### REFERENCES

- [1] L.M. Filanovsky and Y.F. Chan, "BiCMOS Cascaded Bandgap Voltage Reference," in Circuits and Systems, 1996., IEEE 39th Midwest symposium on, 1996, PP: 943-946.

- [2] M. Ferro, F. Salerno and R. Castello, "A Floating CMOS Bandgap Voltage Reference For Differential Applications," in Solid-State Circuits Conference (ESSCIRC '88) Fourteenth European, 1988, Manchester, pp: 219-222

- [3] M. D. Ker, J. S. Chen and C. Y. Chu, "New Curvature-Compensation Technique for CMOS Bandgap Reference With Sub-1-V Operation," Circuits and Systems II: Express Briefs, IEEE Transactions on, 2006, vol. 53, pp: 667 - 671.

- [4] H. Banba, H.Shiga, A. Umezawa, T. Miyaba, T. Tanzawa, S. Atsumi and K. Sakui, "A CMOS Bandgap Reference Circuit with Sub-1-V Operation," Solid-State Circuits, IEEE Journal of, 1999, vol. 34, pp: 670-674.

- [5] G. Giustolisi, G.Palumbo, M. Criscione and F. Cutri, "A low-voltage low-power voltage reference based on subthreshold MOSFETs," Solid-State Circuits, IEEE Journal of ,2003,vol. 36, pp: 151 154.

- [6] A. J. Annema, "Low-power bandgap voltage references featuring DTMOSTs," Solid-State Circuits, IEEE Journal of, 1999, vol. 34, pp: 949 955.

- [7] H. Neuteboom, B.M.J. Kup and M. Janssens, "A DSP-based hearing instrument IC," Solid-State Circuits, IEEE Journal of, 1997, vol. 32, pp: 1790 - 1806.

- [8] G. Giustolisi and G.Palumbo, Dipt. Elettrico, "A detailed analysis of power-supply noise attenuation in bandgap voltage references" Circuits and Systems I: Fundamental Theory and Applications, IEEE Transactions on, 2003, vol. 50, pp: 185 - 197.

- [9] I. Lee, G. Kim and W. Kim, "Exponential curvature-compensated BiCMOS bandgap references," Solid-State Circuits, IEEE Journal of, 1994, vol. 29, pp: 1396 - 1403.

- [10] G. Rincon-Mora and P.E. Allen, "A 1.1-V current-mode and piecewise-linear curvature-corrected bandgap voltage reference. Solid-State Circuits," IEEE Journal of, 1998, vol. 33, pp: 1551 - 1554.

- [11] Z. Hao, Z. Bo, L. Zhao-ji and L. Ping, "A New CMOS Current Reference with High Order Temperature Compensation," in Communications, Circuits and Systems Proceedings, International Conference on, 2006, pp: 2189-2192.

- [12] G. j. Xie, C. X. Zhang and Y. Y. Zhou, "Design of a Low-power Voltage Reference Based on Subthreshold MOSFETs," in Electronic Computer Technology, International Conference on, 2009, pp: 620-623.

- [13] Z. Qu, M. Zhang, J. Wu and Y. Li, "A Sub-O.6V,34.8nW,4.6ppm/°C CMOS Voltage Reference using Subthreshold and Body Effect Techniques," Microelectronics & Electronics, PrimeAsia Asia Pacific Conference on Postgraduate Research, 2009, pp: 275-278

- [14] A. Adl, k. El-Sankary and E. El-Masry, "Bandgap Reference with Curvature Corrected Compensation Using Subthreshold MOSFETs," in Circuits and Systems(ISCAS), IEEE International Symposium on, 2009, pp: 812-815.

- [15] Y. Li, X. Xia, W. Sun and S. Lu, "A 760mV CMOS Voltage Reference with Mobility and Subthreshold Slope Compensation," in ASIC, (ASICON '09). IEEE 8th International Conference on, 2009, pp: 1145-1148.