# A 60-μW, 98-dB SNDR and 100-dB Dynamic Range Continuous Time Delta Sigma Modulator for Biological Signal Processing in 0.18-μm CMOS

# Hamid Reza Sabouhi<sup>1</sup>, Mohammad Honarparvar<sup>2\*</sup> and Vahid Sabouhi<sup>3</sup>

<sup>1</sup>Department of Electrical Engineering, Islamic Azad University, Jiroft Branch, Jiroft, Iran <sup>2,3</sup>Department of Electrical Engineering, Sahand University of Technology, Tabriz, Iran

# ABSTRACT

This paper presents the design of a high performance micro power modified  $3^{rd}$  order Continuous Time Delta Sigma Modulator intended for digitizing biomedical signals. A distributed feed forward topology is used in order to achieve efficient operation and also the modulator makes use of a Noise Shaping Enhancement (NSE) technique for increasing the performance of the modulator.  $g_m$  over  $I_D$  method is opted for design of the low power analog cells. The modulator operates on the 50 kHz signal bandwidth with sampling frequency of 3.2 MHz and shows 102 dB Signal to Noise + Distortion Ratio (SNDR) in the presence of a wide variety of circuit non-ideal effect including noise in the system level and 98 dB SNDR in the circuit level. This corresponds to an Effective Number of Bits (ENOB) 16 Bits. The modulator dissipation is 60  $\mu$ w so the modulator is suitable for use in low power low cost biomedical instrument.

KEYWORDS: Delta Sigma Modulator, Micro power, Biomedical circuit, gm over ID.

# INTRODUCTION

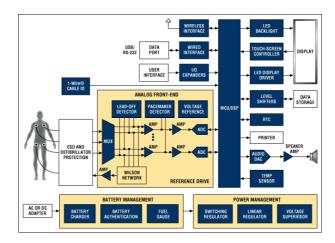

Demand for portable device such as wireless communication systems, battery powered medical devices, etc lead to development of the micro power circuits and analog cells. Since most physiological signals have low amplitude and low frequency the front end IC design is essentially important. These front-end ICs are used for recording the biological signals from a large number of electrodes as shown in Figure 1. According to this figure, analog to digital converter is considered as a part of Application Specific Integrated Circuit (ASIC) for digitizing the biological signals such as electrocardiogram (ECG), Electrocencephalography (EEG) or Electrocardiography (ECOG) waveforms.

Figure 1: Analog front-end for biological signals

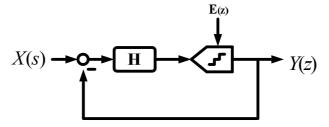

Among the different type of data converters, Delta Sigma modulators (DSMs) are so attractive thanks to the implicit tradeoff between resolution and bandwidth and robustness to circuit imperfections. In fact the DSMs achieve high accuracy data with low accuracy analog blocks<sup>(1)</sup>. The general block diagram of DSM is shown in Figure 2.

\*Corresponding Author: Mohammad Honarparvar, Department of in Electrical Engineering, Sahand University of Technology, Tabriz, Iran.

Figure 2: General block diagram of DSM

According to this block diagram if the loop filters implements in discrete time domain, the DSM is known as DT-DSM and similarly if the loop filters implements in continuous time domain the modulator is named CT-DSM. The use of CT loop filter provides several advantages over DT counterpart such as low Gain Band Width (GBW) requirement of the Operational amplifier in CT compared with DT counterpart which is suitable for low power applications. Also no Anti-Aliasing Filter (AAF) and no RC isolation circuits are required which results in further power saving<sup>(1)</sup>.

Many different type of micro power DSM have been published in the literature. Goes et al. reported a micro power DSM in 0.18  $\mu$ m CMOS. The modulator shows 80 dB SNDR over 10 kHz bandwidth with 200  $\mu$ w power consumption <sup>(2)</sup>. Another micro power modulator with 25 kHz bandwidth by Pun et al. is designed in 0.18  $\mu$ m CMOS process. It shows 74 SNDR with 300  $\mu$ w power consumption <sup>(3)</sup>. Most recently Balagopal et al. presented a DSM with 110  $\mu$ w power consumption in 0.15  $\mu$ m CMOS technology. It achieves 92.4 SNDR over 6 kHz bandwidth with 110  $\mu$ w power consumption <sup>(4)</sup>. As stated in the previous findings, decreasing the power consumption without losses the performance of the modulator is a main challenge. In this research, we are going to design a micro power (less than 100  $\mu$ w) and high performance (more than 90 dB SNDR) CT-DSM.

The object of this paper is to describe the design and simulation of a micro power CT-DSM in both system and circuit level for digitizing the biological signals in the bio instruments. This paper is organized as follow: section 2 explains system level design of the CT-DSM. Section 3 discusses circuit design of the analog cells through  $g_m$  over  $I_D$  method. Simulation results are presented in section 4 and eventually conclusion are given in section 5.

#### 2. CT-DSM System Level Design

This section is addressed system level design of the CT-DSM for biomedical applications. At first a compromise between the modulator parameters is done to select the better choices. Topology selection is considered and explained afterward and the effect of the feed forward topology for low-power design is investigated. A NSE technique is described for increasing the performance of the modulator without increasing the active analog clocks. The effect of non-idealities such as finite op-amp DC gain and finite GBW on the system is also illustrated.

#### 2.1. Parameters Exploration

The Dynamic Range (DR) of the modulator can be calculated by the following equation <sup>(5)</sup>:

$$DR = f(L, OSR, B) = \frac{3}{2} \cdot \frac{2L+1}{\pi^{2L}} \cdot OSR^{2L+1} \cdot (2^B - 1)^2$$

The variables in the above equation include the resolution of the quantizer (B), the loop filter order (L) and the Over Sampling Ratio given by  $OSR = \frac{f_s}{2f_o}$  where  $f_s$  is the sampling frequency

and  $f_{\circ}$  the modulator bandwidth. According to target Signal to Noise Ratio (SNR) of more than 98 dB, the decision of the above system parameters is considered. For more power saving the OSR can be selected as low as possible. The loop filter order can be considered for the modulator stability. Finally it can be seen that modified  $3^{rd}$  order CT with 1 bit internal ADC is a suitable choice to achieve the better performance and low power dissipation for biomedical signals. The OSR is set to 32 for 3.2 MHz sampling frequency.

#### 2.2. Topology Selection

In this design, a single loop low pass modulator topology is selected because of low sensitivity to circuit imperfections compared with MASH structure<sup>(6)</sup>. There are two single loop topology which may be used to implement the proposed CT-DSM. Feed Forward (FF) topology and Feed Back (FB) topology. The FF topology is applied in this design thanks to several reasons: lower swing requirement

for the integrators and higher power efficiency. Also the number of feedback DACs in the FF architecture is less than in the FB topology that lead to lower power dissipation <sup>(7)</sup>.

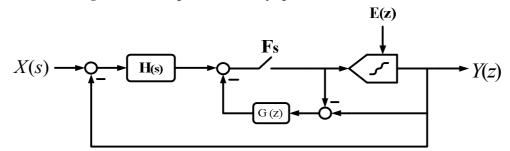

As stated before, reducing the power dissipation is the major challenge in the portable biomedical instrument. To achieve the better power efficiency, reducing the number of integrators can be a solution. A Noise Shaping Enhancement (NSE) technique has been reported that yields a higher order noise shaping with less number of integrators and a successful design is done by this technique in  $^{(8)}$ . In an abbreviated manner, we describe this method. In this technique the DSM increases the noise shaping performance from L<sup>th</sup> order to L+1 <sup>th</sup> order by extraction the quantization noise and injection of quantization noise into the loop filter with one delay cycle. The NSE technique does not change the Signal Transfer Function (STF) of the modulator and the stability of the modulator preserves. Figure 3 shows the block diagram of the NSE-DSM <sup>(9)</sup>.

#### Figure 3: Block diagram of Noise Shaping Enhancement DSM

According to Figure 3, in DT-DSM (H(s) replaced by H (z)), if the noise shaping transfer function (NTF) of conventional modulator and G (z) define by the following formulas:

$NTF(z) = (1 - z^{-1})^{L}$  $G_{ij}(z) = z^{-1} \sum_{k=0}^{N-1} (1 - z^{-1})^{k}$

The Noise Transfer Function of NSE-DSM can be written as following:

$$NTF_{NSE}(z) = NTF(z)[1-G_{ij}(z)]$$

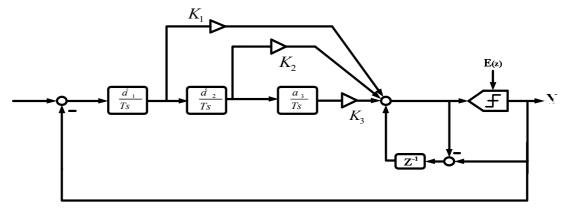

Therefore the order of modulator will be effectively increased just by adding some passive capacitors and switches. Similar to DT-DSM, NSE technique can be applied to increase the noise shaping performance for CT-DSM. In fact if the CT and DT modulator's open loop responses from the sampled quantizer output to the sampled quantizer input are made the same then the modulator exhibit similar close loop dynamic behavior. Combined with above consideration a 3<sup>rd</sup> order CT-DSM with NSE technique is proposed in this design as shown in Figure 4.

Figure 4: Proposed modulator for micro power CT-DSM

A typical NTF of  $(1-Z^{-1})^3$  is chosen for this design and coefficients of the CT-DSM is calculated as a function of the DT integrator coefficient by using the impulse invariant transform. The coefficients of the CT-DSM for None Return to Zero (NRZ) DAC pulse shaping are listed in Table 1.

## 2.3. Integrator Output Scaling

Saturation of the integrators is a challenge in the DSM, if the output voltage level of integrators becomes too large. To solve this problem a scaling coefficients is done for this design to serve a reasonable signal swing at each integrator output<sup>(10)</sup>. This scaling procedure can be expressed in three steps:

1. Divide i<sup>th</sup> gain of integrator by  $\alpha_i$  (called scaling factor)

$$\alpha_i = \frac{OUT_{i-max}}{OUT_{i-desired}}$$

- 2. Distribute  $\alpha_i$  in the modulator to preserve the same NTF

- 3. Perform several iterations to find the scaling factors  $\alpha_i$

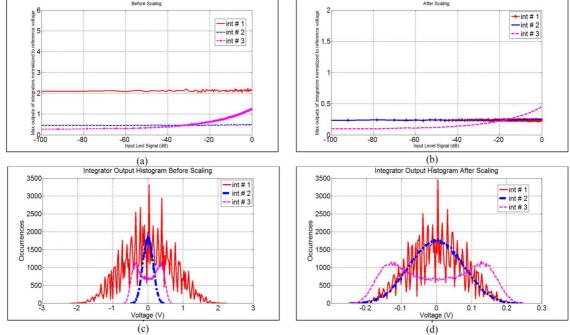

In our design, we select the output swing of  $\frac{V_{ref}}{4}$  for all integrators to achieve 16 bit resolution. Table 1 also shows the final coefficients of the modulators after scaling for the proposed design and Figure 5 illustrates the max output swing of integrators versus input signal level and the integrators output histogram before and after scaling. It can be observed from these figures that the output swing of the integrators set to 0.25 of the reference voltage and satisfy the technology requirement.

Table 1:

Coefficients of the modulator before and after scaling

| Coefficients   | K <sub>1</sub> | K <sub>2</sub> | K <sub>3</sub> | a1     | <b>a</b> <sub>2</sub> | <b>a</b> 3 | h <sub>DAC1</sub> |

|----------------|----------------|----------------|----------------|--------|-----------------------|------------|-------------------|

| Before Scaling | 1.84           | 2              | 1              | 1      | 1                     | 1          | 1                 |

| After Scaling  | 16.4171        | 3.8888         | 2.7952         | 0.1117 | 4.6054                | 0.6956     | 1                 |

Figure 5: Max output swing of integrators versus input signal level , before scaling(a) , after scaling(b) integrators output histogram, , before scaling(c) , after scaling(d)

#### 2.4. Non Idealises Effects

A set of behavioral simulations were done in MATLAB / SIMULINK environment to optimize the performance of the modulator and extract the analog building blocks specifications. Also several non-idealities such as finite DC-gain, Gain Band Width (GBW) and sampling jitter were include investigating the effectiveness of these non- idealities on the performance of the modulator. **2.4.1. OTA Requirements**

# Usually in the CT-DSM, the CT-integrator can be implemented by active-RC integrators or Gm-C integrators, in this design we chose active-RC integrators implementation thanks to its high linearity and low noise characteristics. The ideal transfer function of the active-RC integrator can be shown as follow:

$$I(s) = \frac{1}{RCs}$$

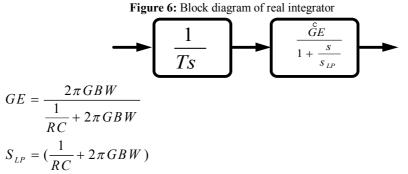

But in real implementation, the OTAs suffer from non-idealities such as the finite DC-gain and finite GBW. Therefore the transfer function of the integrators deviates from its ideal case<sup>(11)</sup>. It can be shown that, the integrator can be modeled as a cascade of ideal integrator and first order low pas filter as illustrated in Figure 6.

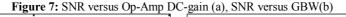

For the proposed design, MATLAB simulations were done to determine the DC-gain and GBW of the OTAs. Figure 7 shows the SNR versus DC-gain and GBW. According to these results a minimum DC-gain of 40dB was chosen for all OTAs and a minimum GBW of  $2f_s$  was selected for the first OTA and  $0.5f_s$  was selected for the second and third OTAs.

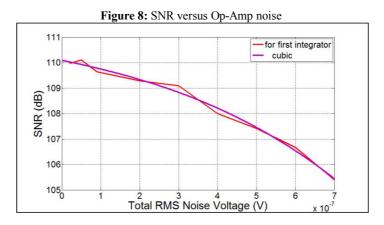

From the stand point of the noise requirement, the design of the first stage of the DSM is more critical because the noise of the first OTA is directly added to the signal without any attenuation. Op-Amp noise modeling was performed in this design similar to <sup>(12)</sup>. The total rms noise voltage includes effects from wideband thermal noise, flicker noise and DC offset. Figure 8 shows the SNR versus the total rms noise voltage.

#### 2.4.2. Sampling Jitter and Excess Loop Delay

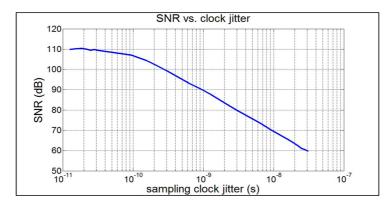

The effects of clock jitter and excess loop delay on a CT-DSM are two major key issues. Due to low sampling frequency and negligible comparator delay, the effect of excess loop delay is not more sensitive. Commonly the noise due to the clock jitter sets a sever SNR degradation for a CT-DSM. Figure 9 shows the SNR versus the sampling jitter. In this case 7 ps sampling jitter is acceptable in order to not severely degrade the performance.

Figure 9: SNR versus sampling jitter

#### 3. CT-DSM Circuit Level Design

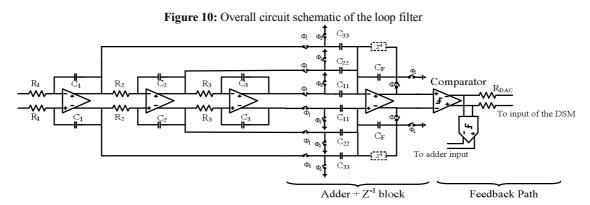

The design of modulator is an iterative process between system level and circuit level. The overall circuit schematic of the modified  $3^{rd}$  order CT-DSM is illustrated in the Figure 10. The modulator is designed in TSMC 0.18  $\mu$ m CMOS process with 1.8 V supply voltage. The implementation of each block of CT-DSM including Loop Filters, Comparator as a quantizer and active adder with SC circuitry is investigated in this section.

#### 3.1. Loop Filter Design

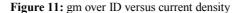

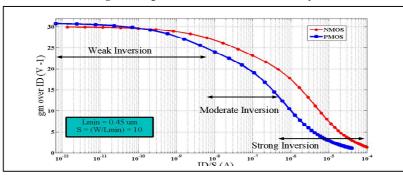

As stated before the power consumption is a major challenge in the biomedical instrument. A power saving can be done by a proper design in both system and circuit level. In the system level, a NSE technique considered for low power design. But there are several techniques in the process level for designing low voltage low power circuits such as voltage boosting technique, floating gate technique, sub-threshold technique <sup>(13)</sup>. A sub threshold technique based on g<sub>m</sub> over I<sub>D</sub> method is opted for designing OTA used in the integrators. The design methodology based on g<sub>m</sub> over I<sub>D</sub> characteristic proposed by <sup>(14)</sup> allows a unified synthesize methodology in the strong inversion, moderate inversion and weak inversion. In this method a relationship between the ratios of the transconductance (g<sub>m</sub>) over the normalized drain current ( $\frac{I_D}{s}$ ) is considered to explore the design space as shown in Figure 11. According to this figure, when the maximum available current determined, we can achieve ( $\frac{I_D}{s}$ ) for the corresponding ( $\frac{g_m}{I_D}$ ). More details will present in the next subsection.

#### 3.1.1. First Integrator Design

First integrator is known as a golden integrator. The power consumption of this integrator is the major contributor to the overall power consumption in the DSM. There is much architecture available. Some of the commonly used architectures are compared in Table 2 <sup>(15)</sup>. In order to combine the high gain and low power requirement a Telescopic OTA is selected for the first integrator. It is necessary to mention that the Telescopic OTA suffers from the limit output swing compared to Folded Cascode OTAs and Two Stage OTAs. In our design voltage scaling has been down in the system level to guarantee the output swings of the integrators are not too large.

| Та             | able 2: | Commonly used an | rchitecture ( | DTAs            |         |                      |

|----------------|---------|------------------|---------------|-----------------|---------|----------------------|

| Topology       |         |                  | Gain          | Output<br>Swing | Speed   | Power<br>Consumption |

| Telescopic     |         |                  | Medium        | Medium          | Highest | Lowest               |

| Folded Cascode |         |                  | Medium        | Medium          | High    | Medium               |

| Two Stage      |         |                  | High          | Highest         | Low     | Medium               |

| Gain Boosted   |         |                  | High          | Medium          | Medium  | High                 |

The operating modes of MOS can be separated into the following modes [14]:

- 1. Weak inversion mode (known as the sub-threshold)

- 2. Moderate inversion

- 3. Strong inversion

Re We

As shown in Figure 11. The features of each region are summarized in Table 3.

|               | I able 3 | : Operatin       | g mod  | es of M             | 05               | FEIS    |          |     |         |        |     |     |

|---------------|----------|------------------|--------|---------------------|------------------|---------|----------|-----|---------|--------|-----|-----|

| egion         | Features | S                |        |                     |                  |         |          |     |         |        |     |     |

| eak Inversion | higher t | ransconductance, | larger | g <sub>m</sub> over | I <sub>D</sub> , | smaller | current, | low | thermal | noise, | low | GBW |

|                    | applications                                                                                        |

|--------------------|-----------------------------------------------------------------------------------------------------|

| Strong Inversion   | a compromise between the low power consumption of weak inversion and high speed of strong inversion |

| Moderate Inversion | smaller g <sub>m</sub> over I <sub>D</sub> , high GBW application                                   |

On such a such as a CMOREET

As illustrated in Figure 11 and Table 3, the weak inversion is more suitable for low power design because it provides higher  $g_m$  over  $I_D$  with smaller current.

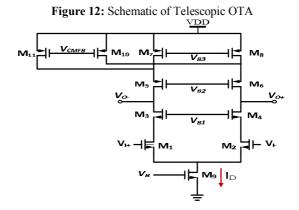

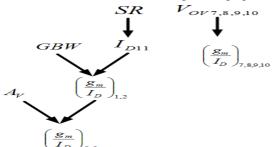

Figure 12 shows the schematic of Telescopic OTA. According to this figure MOSFETs  $M_1 - M_4$  are the core of the OTA and  $M_5 - M_8$  role as load and finally  $M_9$  provide the DC-bias current. The open loop gain and the GBW of the OTA are given by the following formulas.

$$GBW = \frac{g_{m1}}{2\pi C_L} = \frac{g_{m1}}{I_D} \cdot \frac{I_D}{2\pi C_L}$$

$$A_v = \frac{g_{m1}}{I_D} \cdot \frac{g_{m3}}{I_D} \cdot (\frac{1}{\lambda_n^2 + \lambda_p^2})$$

Where,  $gm_1$  and  $gm_3$  are respectively the transconductances of transistors  $M_1$  and  $M_3$ .  $I_D$  is the bias current flowing in MOSFETs  $M_1$ ,  $M_2$ , and  $M_9$ .  $C_L$  is the capacitance at the output node,  $\lambda_N$  and  $\lambda_P$  are the parameters related to channel length modulation respectively for NMOS and PMOS devices. This OTA is designed based on the  $\left(\frac{gm}{I_D}\right)$  procedure reported by Silveira. The design flow of this strategy is shown in Figure 13 and the performance summary is listed in Table 4.

Figure 13: Telescopic OTA design flow graph

Table 4: Telescopic OTA specifications

| Telescopic OTA characteristic<br>(first stage) | value           |

|------------------------------------------------|-----------------|

| Dc-gain<br>GBW                                 | 50 dB<br>10 MHz |

| Phase Margin                                   | $68^{\circ}$    |

| SR                                             | 1.5V/µs         |

| Power                                          | 20 µW           |

# 3.1.2. Second and Third Integrator Design

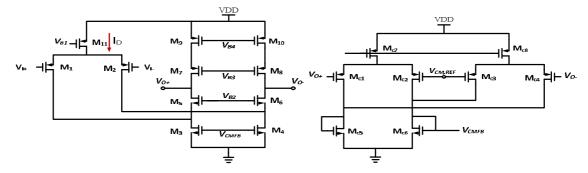

Since the choice of the input common mode level is easier for the folded cascode OTA, this topology is selected for second and third stages <sup>(15)</sup>. On the other hand, these stages are relatively less critical than the first stage therefore the current is scaled down to reduce power consumption. Figure 14 shows the folded cascode OTA and its CMFB. For this OTA the open loop gain and GBW are given by:

$$GBW = \frac{g_{m1}}{C_L} = \frac{g_{m1}}{I_D} \cdot \frac{I_D}{C_L}$$

$$A_V = \frac{g_{m1} \cdot g_{m6} \cdot g_{m8}}{I_D^2 (g_{m8} \lambda_n^2 + g_{m6} \lambda_p^2)} \Big|_{g_{m6} = g_{m8}} = \frac{g_{m1} \cdot g_{m6}}{I_D^2 (\lambda_n^2 + \lambda_p^2)}$$

Figure 14: Schematic of Folded Cascode OTA and CMFB

Also  $g_m$  over  $I_D$  method is applied to this topology for determining the dimensions of the MOSFETs. Figure 15 indicates the design flow of the folded cascode OTA through  $g_m$  over  $I_D$  method and Table 5 shows the specifications of the designed folded cascode OTA.

Table 5: Folded cascode OTA specifications

| Folded cascode OTA characteristic (second and third stages) | value          |

|-------------------------------------------------------------|----------------|

| Dc-gain<br>GBW                                              | 53 dB<br>3 MHz |

| Phase Margin                                                | 63°            |

| SR                                                          | 1V/μs          |

| Power                                                       | 13.5 μW        |

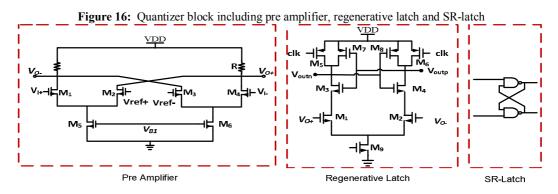

#### 3.2. Preamplifier and Comparator Design

The schematic of the 1 bit quantizer including pre amplifier, regenerative latch and SR latch used in the proposed micro power CT-DSM is shown in Figure 16. Because of decreasing the offsets and kick-back noise from the latch a Differential Difference Amplifier (DDA) with resistive loads is used for the pre amplifier. A dynamic regenerative latch is used because it is a power efficient structure<sup>(5)</sup>. The power consumption of the designed comparator is 2.9  $\mu$ w at a 3.2 MHz sampling frequency.

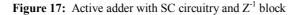

#### 3.3. Active Adder with SC circuitry and one cycle delay block

In the conventional FF topology, an active-R adder uses in the close loop configuration. But in this design, thanks to the  $Z^{-1}$  block, coupling of the quantization error is unpractical. To overcome this problem an active adder using SC circuitry is used as shown in Figure 17. On the other hand, in reality conditions because of the finite GBW of the OTA used in the adder, this adder also introduce excess loop delay that lead to peaking in the magnitude response of the NTF. Macro model simulation shows that an OTA with 20 MHz GBW and 60 dB DC-gain is suitable for implementation of the adder in order to mitigate the NTF peaking and achieve a good performance from the modulator.

Z<sup>1</sup> circuit diagram

#### 4. Modulator Front-End Noise Analysis

The performance of the modulator is degraded because the circuit noise at the modulator front – end is not attenuated. There are three source of noise for the noise of the front end: noise of the two input resistors, noise of the first OTA and eventually noise of  $R_{DAC}$ . The total in band noise caused by the two input resistors and two DAC resistors is:

$$\overline{v}_{R_1}^2 \approx 8kT(R_1 + R_{DAC})2f_{\circ}$$

Under condition  $R_1 = R_{DAC}$  the noise can be expressed as follow:

$$\overline{v}_{R_1}^2 \approx 32kTR_1 f_{\circ} |_{R_1 = R_{D_1}}$$

Where  $k = 1.38 \times 10^{-23}$  J/K (called Boltzmann's coefficient), T is the absolute temperature. In this design we choose R<sub>1</sub>=7.5 kΩ. This value of R<sub>1</sub> generates thermal noise power about 100 dB lower than the full scale input signal.

In the OTA shown in Figure 12 the total in-band thermal noise is given by:

$$\overline{v}_{in,TH}^2 = \frac{16kT\gamma}{g_{m1.2}} \left(1 + \frac{g_{m7,8} + g_{m9,10}}{g_{m1.2}}\right) f_{\circ}$$

And the total in-band flicker noise of the OTA can be expressed as:

$$\overline{v}_{n,\frac{1}{f}}^{2} = \left[\frac{2K_{n}}{(WL)_{1,2}C_{ox}f} + \frac{2K_{p}}{(WL)_{7,8}C_{ox}f} \cdot \frac{g_{m7,8}^{2}}{g_{m1,2}^{2}} + \frac{2K_{p}}{(WL)_{9,10}C_{ox}f} \cdot \frac{g_{m9,10}^{2}}{g_{m1,2}^{2}}\right] Ln(\frac{f_{\text{max}}}{f_{\text{min}}})$$

In the above equations, K represents Boltzmann coefficient, T represents absolute temperature and  $g_m$  represents the transconductance of the OTA. Also  $K_n$  and  $K_p$  represent the flicker noise coefficients of the NMOS and PMOS transistors respectively. According to the above equations the transconductance of  $M_{1,2}$  should be maximized and the transconductance of  $M_{7,8}$  and  $M_{9,10}$  minimized.

## 4. SIMULATION RESULTS

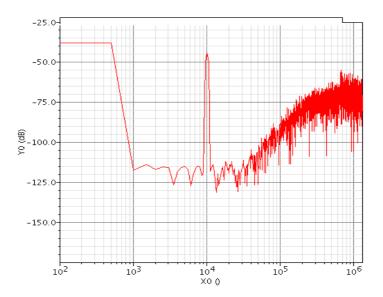

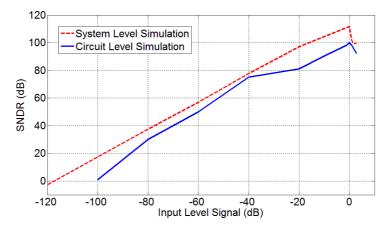

The modulator was simulated in TSMC 0.18  $\mu$ m CMOS technology. Figure 18 illustrates power spectral density of the Delta Sigma Modulator output. The number of samples is 2<sup>16</sup> and the modulator operates at 3.2 MHz clock frequency for the 50 kHz bandwidth. Figure 19 shows both the system level and device level Dynamic Range of the designed Delta Sigma Modulator. According to this curve the modulator shows the peak SNDR of 102dB / 98dB @ -3dBFS in the system and circuit level respectively and the simulated DR is nearly 100dB in the circuit level. The power consumption is measured as 60  $\mu$ w for 1.8 V supply voltage. Performance summary of the designed modulator and several state of the art micro power modulators are shown in Table 6.

#### Figure 18: Simulated power spectral density of modulator

Figure 19: Dynamic range of the micro power CT-DSM in both system level and circuit level

| Table 6: Commonly used architecture OTAS |                                                             |     |                              |                                |               |            |                 |                          |                           |

|------------------------------------------|-------------------------------------------------------------|-----|------------------------------|--------------------------------|---------------|------------|-----------------|--------------------------|---------------------------|

| Ref                                      | Structure                                                   | OSR | Signal<br>bandwidth<br>(kHz) | Sampling<br>frequency<br>(MHz) | SNDR<br>(dB)  | DR<br>(dB) | Process<br>(µm) | Supply<br>voltage<br>(V) | Power consumption<br>(µW) |

| [2]                                      | 2 <sup>nd</sup> order DT<br>– 1bit<br>quantizer             | 256 | 10                           | 5                              | 80            | 83         | 0.18            | 0.9                      | 200                       |

| [3]                                      | 3 <sup>rd</sup> order<br>CT- 1 bit<br>quantizer             | 64  | 25                           | 3.2                            | 74            | -          | 0.18            | 0.5                      | 300                       |

| [4]                                      | 3 <sup>rd</sup> order CT<br>- CIFF                          | 512 | 6                            | 6.144                          | 92.4          | 94.4       | 0.15            | 1.5                      | 110                       |

| This work                                | Modified 3 <sup>rd</sup><br>order CT –<br>1bit<br>quantizer | 32  | 50                           | 3.2                            | 98@-<br>3dBFS | 100        | 0.18            | 1.8                      | 60                        |

#### Table 6: Commonly used architecture OTAs

## 6. DISCUSSION AND CONCLUSION

A micro power Delta Sigma Modulator is presented in this article. Feed forward topology is opted in order to reducing the voltage swing of the integrators that lead to more power saving. A Noise Shaping Enhancement technique is applied for increasing the performance of the modulator without using active analog blocks, so more power saving can be reached.  $G_m$  over  $I_D$  method is used for design of analog building blocks in the sub-micron regime. Two OTAs are separately designed for first stage and other stages respectively. A Telescopic OTA has been used in the first integrator and Folded cascode OTA has been designed in the second and third integrators. This modulator has been simulated in a 0.18-µm TSMC CMOS technology. The simulated SNDR and DR are 98 dB and 100 dB, respectively and the modulator consumed only 60 µW. Although this modulator is designed as a part of CMOS analog front-end IC for portable biomedical applications but final results shows that the proposed modulator is more suitable for audio applications too.

#### REFERENCES

- 1. Ortmanns M. and F. Gerfers, 2006. Continuous-time sigma-delta A/D conversion: Fundamentals, performance limits and robust implementation. vol. 21: Springer Verlag.

- Goes J., B. Vaz, R. Monteiro, and N. Paulino, 2006. A 0.9 V Delta Sigma Modulator with 80dB SNDR and 83dB DR Using a Single-Phase Technique. Solid-State Circuit Conference ISSCC 2006, pp: 191-200.

- Pun K. P., S. Chatterjee, and P. R. Kinget,2007. A 0.5-V 74-dB SNDR 25-kHz continuous-time delta-sigma modulator with a return-to-open DAC. *Solid-State Circuits, IEEE Journal of,* vol. 42, pp: 496-507.

- 4. Balagopal S., R. M. Roy, and V. Saxena, 2010. A 110W Single-Bit Continuous-Time ΔΣ Converter with 92.5 dB Dynamic Range. Circuits and Systems Workshop (DCAS), 2010 IEEE Dallas.

- 5. Schreier R., G. C. Temes, I. o. Electrical, and E. Engineers, 2005. *Understanding delta-sigma data converters*: IEEE press New Jersey.

- Chen F., T. Kuendiger, S. Erfani, and M. Ahmadi, 2008. Design of a wideband low-power continuous-time ΣΔ modulator in 90 nm CMOS technology. *Analog Integrated Circuits and Signal Processing, Springer*, vol. 54, pp. 187-199, 2008.

- 7. Chen X., Y. Wang, Y. Fujimoto, P. Lo Re, Y. Kanazawa, J. Steensgaard, and G. Temes, 2007. A 18 mW CT ΔΣ modulator with 25 MHz bandwidth for next generation wireless applications. Custom Integrated Circuits Conference, CICC '07. IEEE, pp: 73-76.

- 8. Honarparvar M., E. N. Aghdam, M. Shamsi, A. Zahedi, and M. Zafaranchi, 2011. A Low Power, High Performance Multi-Mode Delta-Sigma ADC for GSM, WCDMA and WLAN Standards. Electronic Devices, Systems and Applications (ICEDSA).

- Lee K., M. Bonu, and G. Temes, 2006. Noise-coupled ΔΣ ADC's. *Electronics Letters*, vol. 42, pp: 1381-1382.

- Beilleau N., H. Aboushady, and M. Louërat, 2003. Systematic approach for scaling coefficients of discrete-time and continuous-time sigma-delta modulators. Circuits and Systems, IEEE 46th Midwest Symposium on, pp. 233-236.

- Ortmanns M., F. Gerfers, and Y. Manoli, 2003. Influence of finite integrator gain bandwidth on continuous-time sigma delta modulators. Circuits and Systems, ISCAS '03. Proceedings of the 2003 Circuits and Systems, ISCAS '03. Proceedings of the 2003 International Symposium on pp: I-925-I-928 vol. 1.

- Brigati S., F. Francesconi, P. Malcovati, D. Tonietto, A. Baschirotto, and F. Maloberti, 1999. Modeling sigma-delta modulator non-idealities in SIMULINK (R). Circuits and Systems. ISCAS '99. Proceedings of the 1999 IEEE International Symposium on pp. 384-387 vol. 2.

- 13. Jinghua ZH., 2010. Low-voltage low-power continuous-time delta-sigma modulator designs. Ph.D. thesis, NUS University.

- 14. F. Silveira, D. Flandre, and P. Jespers, 1996. A gm/ID based methodology for the design of CMOS analog circuits and its application to the synthesis of a silicon-on-insulator micropower OTA. *Solid-State Circuits, IEEE Journal of,* vol. 31, p: 1314-1319.

- 15. Razavi B., 2001. *Design of Analog CMOS Integrated Circuits. ser*: McGraw-Hill Series in Electrical and Computer Engineering. New York, USA: McGraw-Hill.